## EE 435

#### Lecture 23

#### Layout of Analog Circuits (brief) Common Mode Feedback Circuits

#### Review from last lecture Model Parameter Variation

Correspondingly:

## Random Offset Voltages

$$\sigma_{V_{OS}}^{2} = 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} + \frac{V_{EBn}^{2}}{4} \left( \frac{1}{W_{n}L_{n}} A_{\mu_{n}}^{2} + \frac{1}{W_{p}L_{p}} A_{\mu_{p}}^{2} + A_{COX}^{2} \left[ \frac{1}{W_{n}L_{n}} + \frac{1}{W_{p}L_{p}} \right] \right) + 2A_{L}^{2} \left[ \frac{1}{W_{n}L_{n}^{2}} + \frac{1}{W_{p}L_{p}^{2}} \right] + A_{w}^{2} \left[ \frac{1}{L_{n}W_{n}^{2}} + \frac{1}{L_{p}W_{p}^{2}} \right] \right) \right]$$

which again simplifies to

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTO n}^{2}}{W_{n} L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n} L_{p}^{2}} A_{VTO p}^{2} \right]$$

Note these offset voltage expressions are identical!

#### **Random Offset Voltages**

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTO\,n}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTO\,p}^{2} \right]$$

This expression has somewhat peculiar coefficients. The first term on the right is dependent upon the reciprocal of the area of the n-channel device but the corresponding coefficient on the second term on the right appears to depend upon the dimensions of both the n-channel and p-channel devices. But this can be rewritten as

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTO\,n}^{2}}{W_{n}L_{n}} + \left( \frac{V_{EB\,n}}{V_{EB\,p}} \right)^{2} \frac{A_{VTO\,p}^{2}}{W_{p}L_{p}} \right]$$

The dependence of the variance on the area of the n-channel and p-channel devices is more apparent when written in this form.

### Source of Random Offset Voltages

The random offset voltage is almost entirely that of the input stage in most op amps

#### **Random Offset Voltages**

It can be shown that

$$\sigma_{V_{OS}}^{2} \simeq 2V_{t}^{2} \left[ \frac{A_{Jn}^{2}}{A_{En}} + \frac{A_{Jp}^{2}}{A_{Ep}} \right]$$

where very approximately

$$A_{Jn} = A_{Jp} = 0.1\mu$$

#### **Random Offset Voltages**

Typical offset voltages:

MOS - 5mV to 50MV BJT - 0.5mV to 5mV

These can be scaled with extreme device dimensions

Often more practical to include offset-compensation circuitry

# **Common Centroid Layouts**

Almost Theorem:

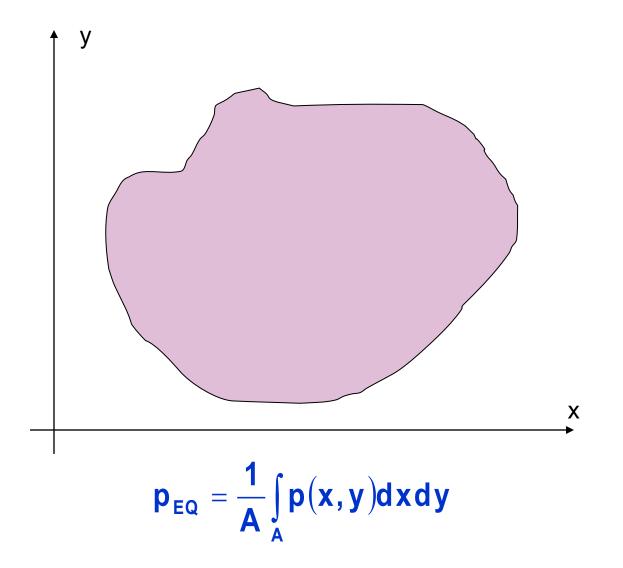

If p(x,y) varies linearly throughout a two-dimensional region, then  $p_{EQ}=p(x_0,y_0)$  where  $x_0,y_0$  is the geometric centroid to the region.

If a parameter varies linearly throughout a two-dimensional region, it is said to have a linear gradient.

Many parameters have a dominantly linear gradient over rather small regions but large enough to encompass layouts where devices are ideally matched

#### Review from last lecture Common Centroid Layouts

$(x_0, y_0)$  is geometric centroid

$$p_{EQ} = \frac{1}{A} \int_{A} p(x, y) dx dy$$

If  $\rho(x,y)$  varies linearly in any direction, then the theorem states

$$p_{EQ} = \frac{1}{A} \int_{A} p(x,y) dx dy = p(x_0,y_0)$$

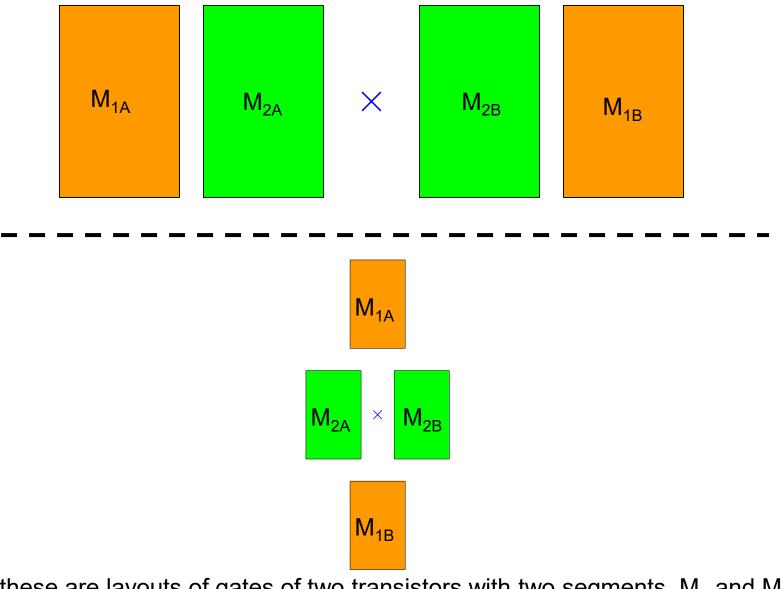

#### **Common Centroid of Multiple Segmented Geometries**

If these are layouts of gates of two transistors with two segments,  $M_1$  and  $M_2$  have common centroids. They are thus termed common-centroid layouts

**Review from last lecture** Common Centroid Layout Surrounded by **Dummy Devices**

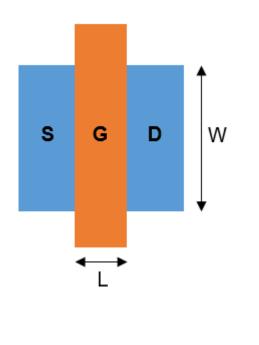

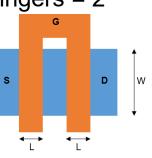

### Fingers and Multipliers

- Multiple fingers use shared diffusions •

- Multipliers refer to multiple copies of transistors with individual drains ٠ and sources

Important to match orientation if overall device matching is required

s

D

s

w

Multiplier = 2

Leff=2L, Weff=W

W

Leff=L, Weff=2W https://electronics.stackexchange.com/questions/246463/multiple-fingers-vs-single-ringer-layout-moster-transistor

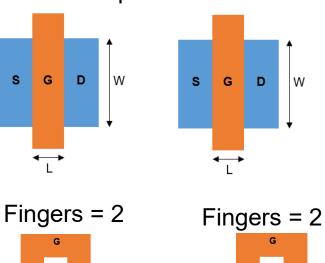

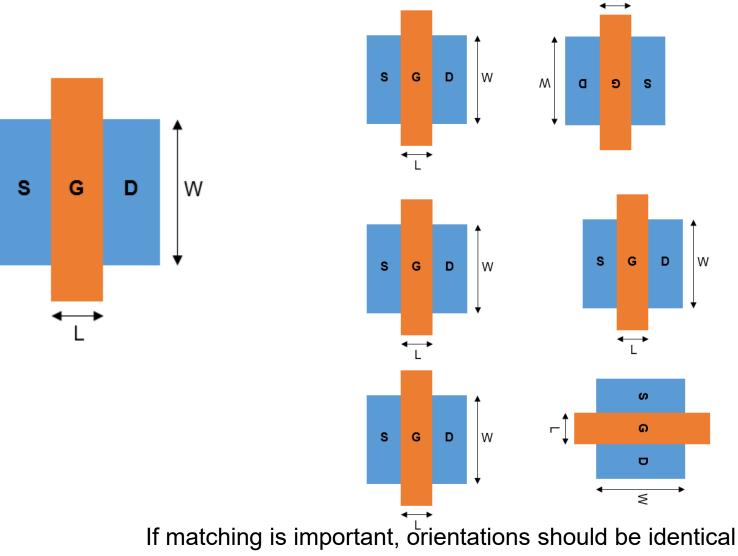

#### Fingers and Multipliers

**Alternate Orientations**

٦.

W

https://electronics.stackexchange.com/questions/246463/multiple-fingers-vs-single-finger-layout-mosfet-transistor

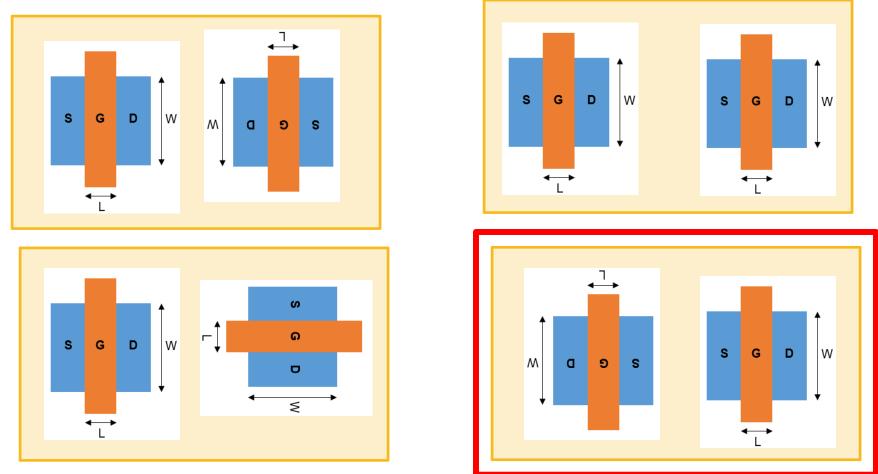

### **Fingers and Multipliers**

**Alternate Orientations**

Which layout would be best for the critical differential input pair in an operational amplifier?

Of course, a common-centroid variant would likely be used !

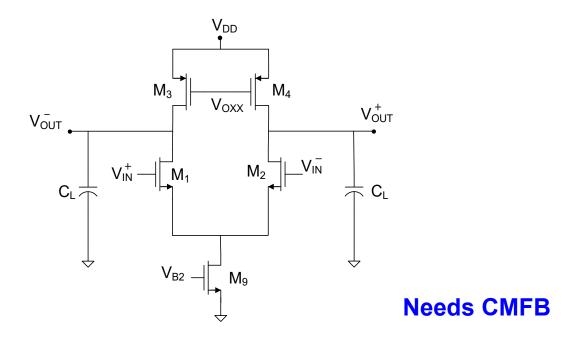

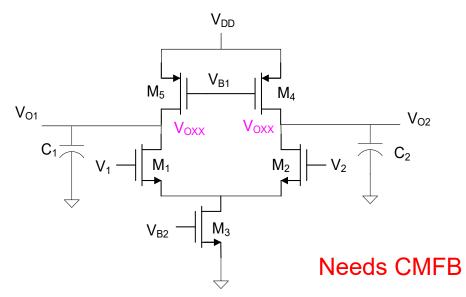

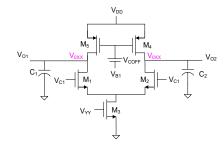

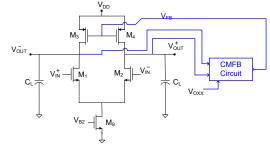

## Common-Mode Feedback

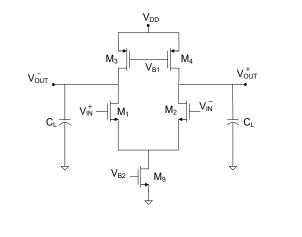

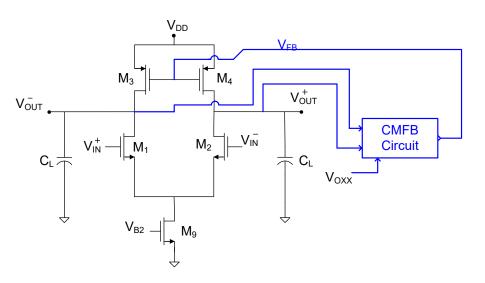

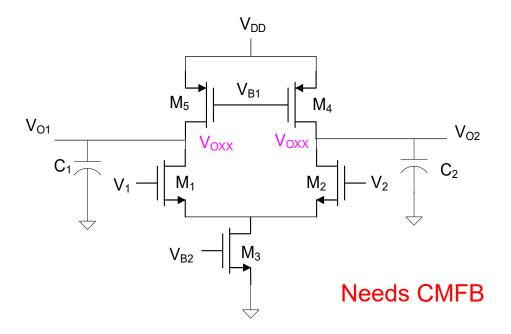

Repeatedly throughout the course, we have added a footnote on fullydifferential circuits that a common-mode feedback circuit (CMFB) is needed for some circuits

If required, the CMFB circuit establishes or "stabilizes" the operating point or operating points of the op amp

## Common-Mode Feedback

On the reference op amp, the CMFB signal can be applied to either the pchannel biasing transistors or to the tail current transistor

It is usually applied only to a small portion of the biasing transistors though often depicted as shown

There is often considerable effort devoted to the design of the CMFB though little details are provided in most books and the basic concepts of the CMFB are seldom rigorously developed and often misunderstood

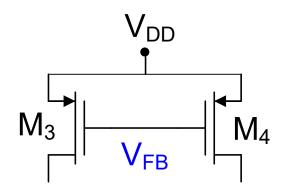

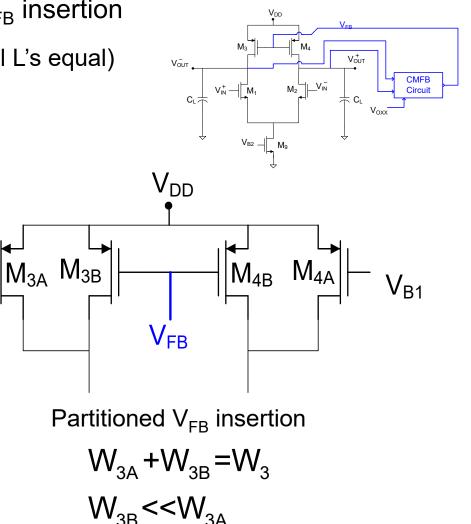

# Common-Mode Feedback

Partitioning biasing transistors for V<sub>FB</sub> insertion

(Nominal device matching assumed, all L's equal)  $V_{DD}$

$M_3$   $V_{B1}$   $M_4$

Ideal (Desired) biasing

$V_{\text{FB}}$  insertion

Of course L/R symmetry is assumed

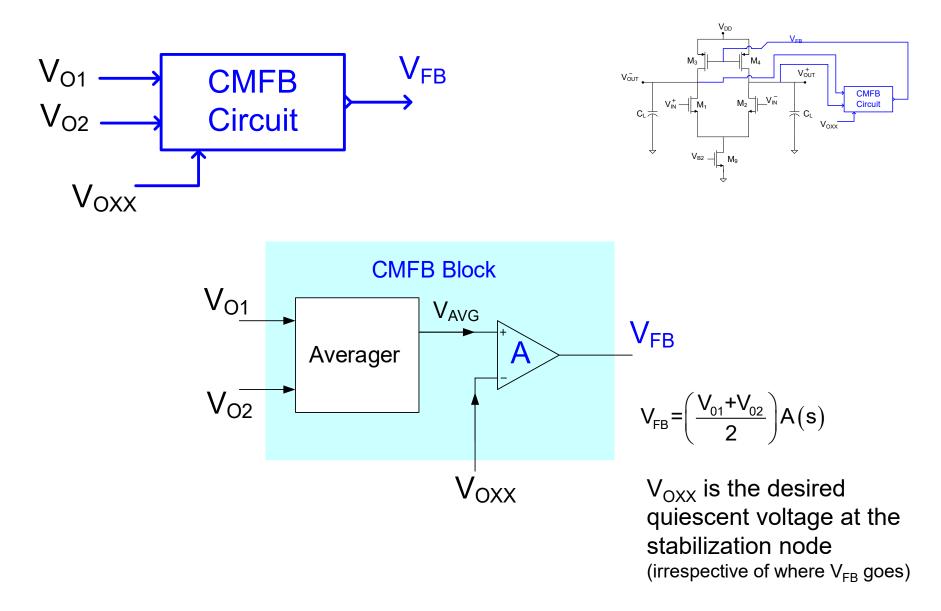

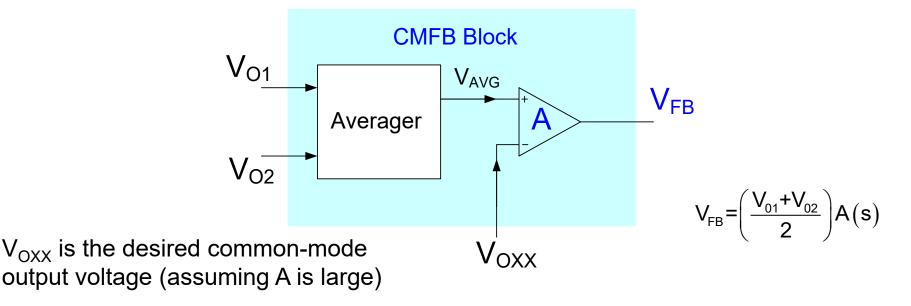

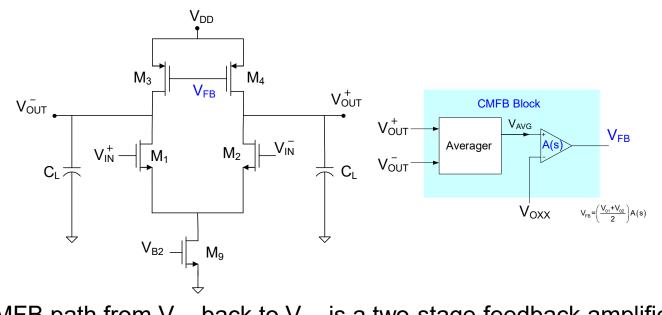

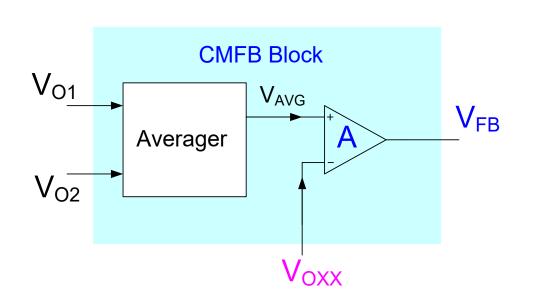

#### **Basic Operation of CMFB Block**

#### **Basic Operation of CMFB Block**

- Comprised of two fundamental blocks

Averager

Differential amplifier

- Sometimes combined into single circuit block

- CMFB is often a two-stage amplifier so compensation of the CMFB path often required !!

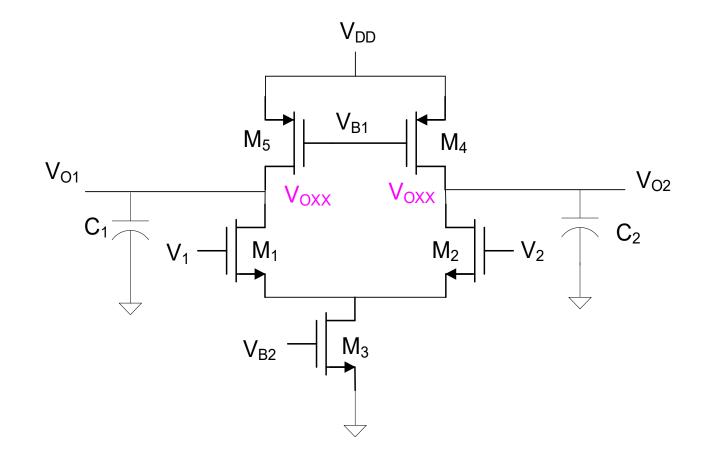

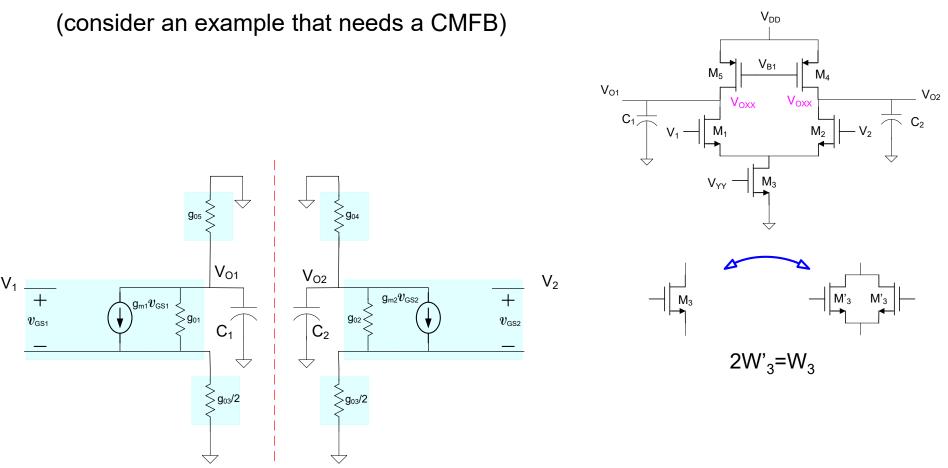

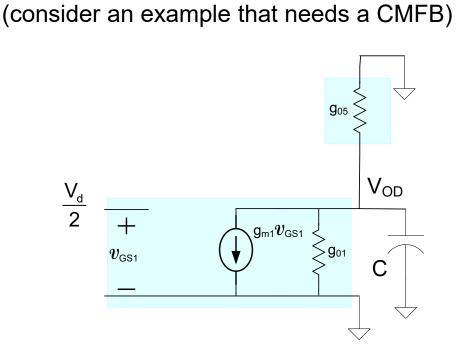

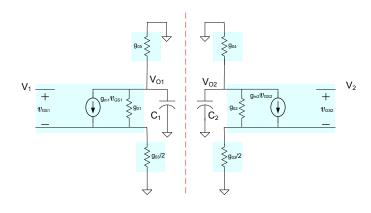

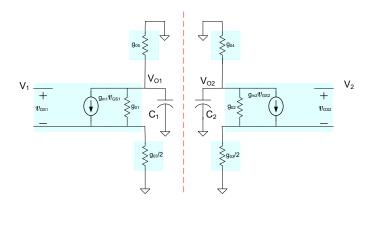

(consider an example that needs a CMFB)

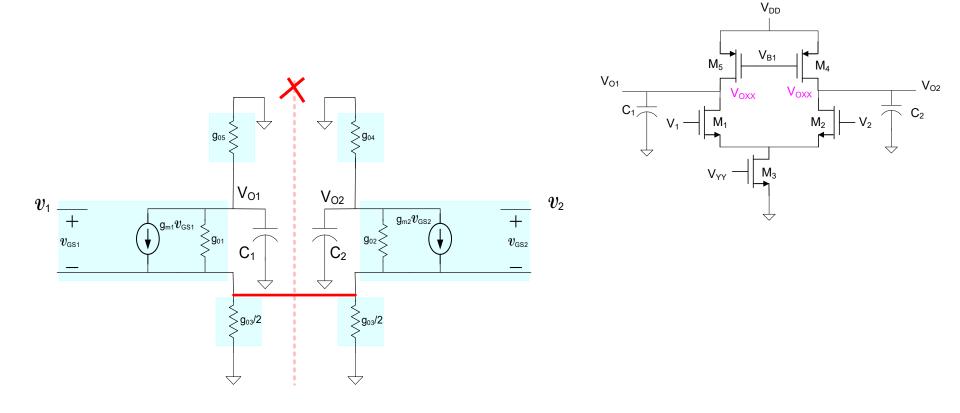

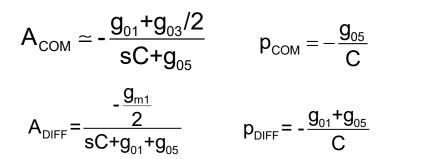

Notice there are two capacitors and thus two poles in this circuit

Small-signal model showing axis of symmetry (for  $V_1 = V_2 = V_{INQ}$  i.e.  $v_1 = v_2 = 0V$ )

What order transfer functions are expected (note two capacitors!)?

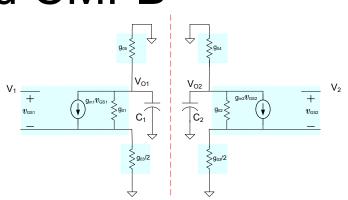

Small-signal difference-mode half circuit

$$V_{OD} \left( sC + g_{01} + g_{05} \right) + g_{m1} \frac{V_d}{2} = 0$$

$$A_{DIFF} = \frac{-\frac{g_{m1}}{2}}{sC + g_{01} + g_{05}}$$

$$p_{DIFF} = -\frac{g_{01} + g_{05}}{2}$$

С

Note there is a single-pole in this circuit

What happened to the other pole?

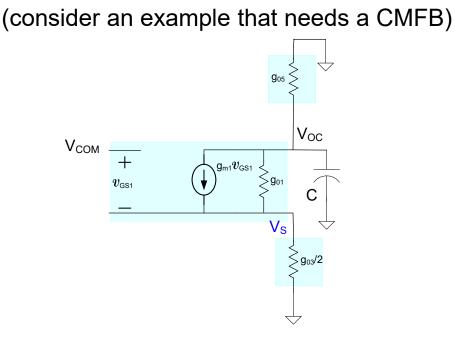

Standard small-signal common-mode half circuit

$V_{OC}(sC+g_{01}+g_{05})+g_{m1}(V_{COM}-V_{S})=0$  $V_{S}(g_{01}+g_{03}/2)-g_{m1}(V_{COM}-V_{S})=V_{OC}g_{01}$

$$\begin{split} A_{\text{COM}} = & \frac{-g_{\text{m1}}(g_{01} + g_{03}/2)}{\left(sC + g_{01} + g_{05}\right)\left(g_{\text{m1}} + g_{01} + g_{03}/2\right) - g_{\text{m1}}g_{01}} \cong -\frac{g_{01} + g_{03}/2}{sC + g_{05}} \\ p_{\text{COM}} = & -\frac{g_{05}}{C} \end{split}$$

Note there is a single-pole in this circuit

And this is different from the difference-mode pole

But the common-mode gain tells little, if anything, about the CMFB

Second-order gain functions would have occurred had we not created symmetric half-circuits by assuming  $v_1 = v_2$

(consider an example that needs a CMFB)

- Difference-mode analysis of symmetric circuit completely hides all information about common-mode

- This also happens in simulations

- Common-mode analysis of symmetric circuit completely hides all information about difference-mode

- This also happens in simulations

- Difference-mode poles may move into RHP (for two-stage structures) with FB so compensation is required for proper operation (or stabilization)

- Common-mode poles may move into RHP (for two-stage structures) with FB so compensation is required for proper operation (or stabilization)

- Difference-mode simulations tell nothing about compensation requirements for common-mode feedback

- Common-mode simulations tell nothing about compensation requirements for difference-mode feedback

$g_{m2}v_{GS2}$

$v_{\scriptscriptstyle {\rm GS2}}$

(consider an example that needs a CMFB)  $A_{COM} \simeq -\frac{g_{01} + g_{03}/2}{sC + g_{05}}$   $p_{COM} = -\frac{g_{05}}{C}$   $V_1 = -\frac{g_{05}}{C}$   $A_{DIFF} = -\frac{g_{m1}}{2}$   $p_{DIFF} = -\frac{g_{01} + g_{05}}{C}$

- Common-mode and difference-mode gain expressions often include same components though some may be completely absent in one or the other mode

- Compensation capacitors can be large for compensating either the common-mode or difference-mode circuits

- Highly desirable to have the same compensation capacitor serve as the compensation capacitor for both difference-mode and common-mode operation

- But tradeoffs may need to be made in phase margin for both modes if this is done

- Better understanding of common-mode feedback is needed to provide good solutions to the problem

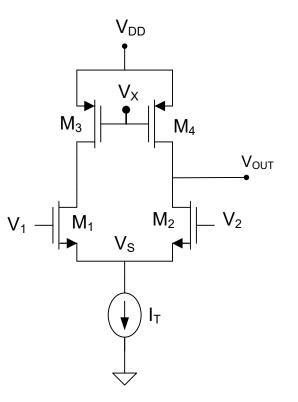

#### Does this amplifier need compensation?

No – because it is a single-stage amplifier ?

The difference-mode circuit of this 5T op amp usually does not need compensation ?

But what about the common-mode operation?

No – because the common-mode circuit is also a single-stage circuit?

What are the common-mode inputs for CMFB?  $V_{B1}$  or  $V_{B2}$

But observe that the common-mode inputs  $V_{1C}$  and  $V_{2C}$  are not the common-mode inputs for the CMFB?

#### Does this amplifier need compensation?

This circuit has 3 different natural common-mode inputs:

$$V_{B1}, V_{B2}, \frac{V_1 + V_2}{2}$$

$V_{B1} \text{ or } V_{B2} \,$  (or possibly both in some way) are the inputs for CMFB

Can it be argued that it is still a single-stage common-mode circuit irrespective of which common-mode input is used and thus compensation of the common-mode circuit will not be required?

#### Does this amplifier need compensation?

The CMFB path from V<sub>FB</sub> back to V<sub>FB</sub> is a two-stage feedback amplifier comprised of the common-mode gain of the basic 5T circuit from V<sub>FB</sub> to V<sub>OUT</sub> and the common-mode gain from V<sub>OUT</sub> to V<sub>FB</sub>

This amplifier needs compensation (of the CMFB path) even if the basic amplifier is single-stage

The overall amplifier including the  $\beta$  amplifier for the differential feedback path should be considered when compensating the CMFB circuit

If a second-stage is added to the 5T op amp, the compensation network for the differential stage <u>may</u> also provide the needed compensation for the CMFB path

#### **Common-Mode and Difference-Mode Issues**

Overall poles are the union of the common-mode and difference mode poles

Separate analysis generally required to determine common-mode and difference-mode performance

Some amplifiers will need more than one CMFB

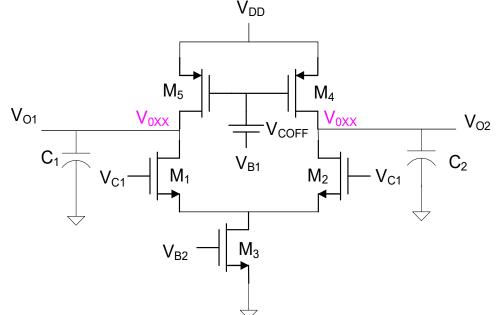

## Common-mode offset voltage

Assume ideally  $V_{B1}$  will provide the desired value for  $V_{OXX}$

Definition: The common-mode offset voltage is the voltage that must be applied to the biasing node at the CMFB point to obtain the desired operating point at the stabilization node

Note: Could alternately define common-mode offset relative to  $V_{\rm B2}$  input if CMFB to  $\rm M_3$

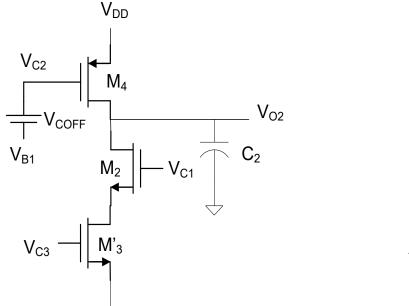

# Common-mode offset voltage

Consider again the Common-mode half circuit

There are three common-mode inputs to this circuit !

The common-mode signal input is distinct from the input that is affected by  $V_{COFF}$ The gain from the common-mode input where  $V_{FB}$  is applied may be critical ! How do the poles from the three different CM inputs relate to each other?

They are the same!!

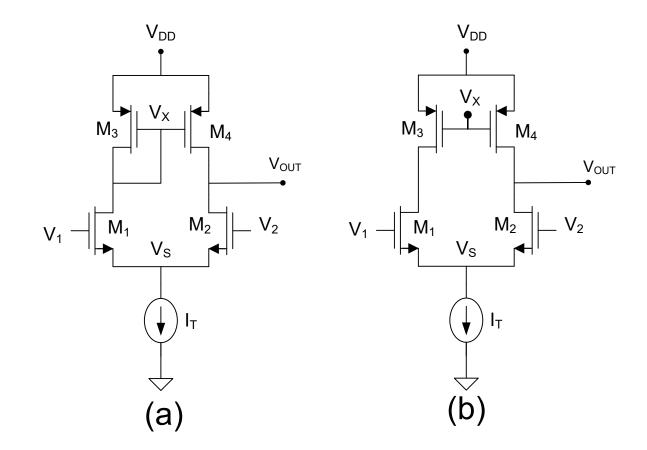

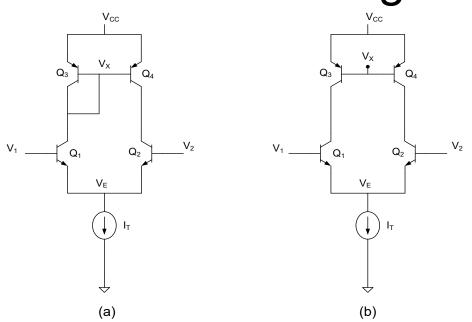

## Common-mode gains

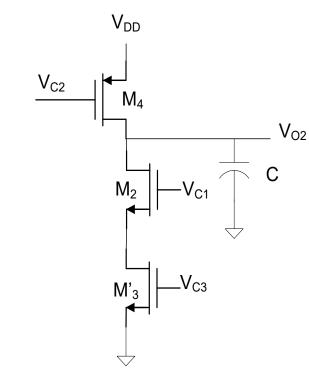

$$A_{COM} = \frac{V_{02}}{V_{C1}} \cong -\frac{g_{02} + g_{03}/2}{sC + g_{04}}$$

$$A_{COM2} = \frac{V_{02}}{V_{C2}} \cong -\frac{g_{m4}}{sC + g_{04}}$$

$$A_{COM3} = \frac{V_{02}}{V_{C3}} \cong -\frac{g_{m3}/2}{sC + g_{04}}$$

$A_{\text{COM0}} \cong -\frac{g_{02} + g_{03}/2}{g_{04}} = -\frac{\lambda I_T}{\lambda I_T/2} = -\frac{1}{2}$  $A_{\text{COM20}} \cong -\frac{g_{m4}}{g_{04}} = -\frac{2I_T/V_{EB4}}{\lambda I_T/2} = -\frac{4}{V_{EB4}\lambda}$  $A_{\text{COM30}} \cong -\frac{g_{m3}/2}{g_{04}} = -\frac{V_{EB3}}{\lambda I_T/2} = -\frac{2}{\lambda V_{EB3}}$

Although the common-mode gain  $A_{COM0}$  is very small,  $A_{COM20}$  is very large! (but can be reduced by partitioning  $M_4$ )

Shift in  $V_{02Q}$  from  $V_{OXX}$  is the product of the common-mode offset voltage and  $A_{COM20}$

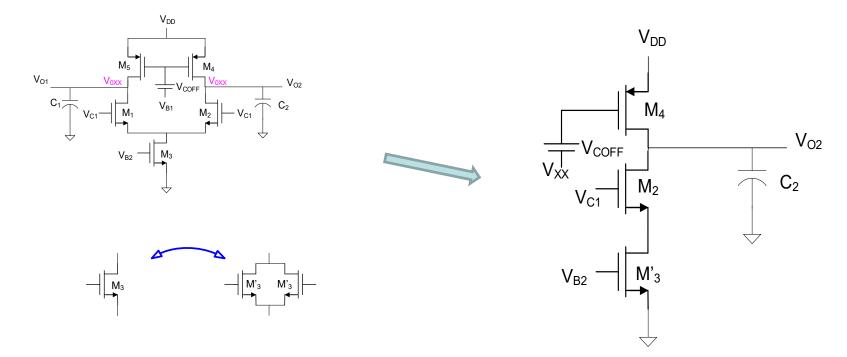

#### Effect of common-mode offset voltage

$$\mathsf{A}_{\mathsf{COM20}} \cong -\frac{4}{V_{\textit{EB5}}\lambda}$$

$\Delta V_{02} = A_{\rm COM20} V_{\rm COFF}$

How much change in  $V_{02}$  is acceptable? (assume e.g. 50mV)

How big is  $V_{COFF}$ ? (similar random expressions for  $V_{OS}$ , assume, e.g. 25mV) (that due to process variations even larger) How big is  $A_{COM20}$ ? (if  $\lambda$ =.01,  $V_{EB}$ =.2,  $A_{COM20}$ =2000) If change in  $V_{02}$  is too large, CMFB is needed (50mV >? 2000x25mV)

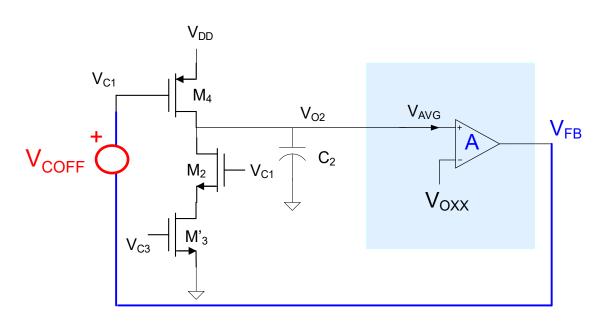

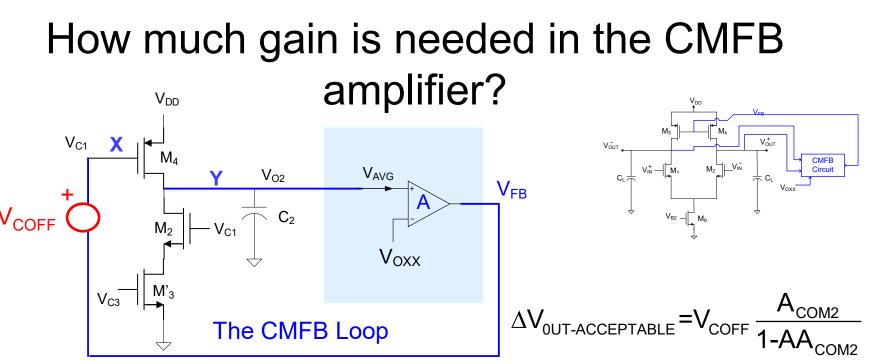

# How much gain is needed in the CMFB amplifier?

V<sup>+</sup><sub>OUT</sub>

CMFB Circuit

CMFB must compensate for  $V_{COFF}$

Want to guarantee  $|V_{02Q}-V_{0XX}| < \Delta V_{OUT-ACCEPTABLE}$

This is essentially the small-signal output with a small-signal input of V<sub>COFF</sub>

# How much gain is needed in the CMFB amplifier?

Want to guarantee  $|V_{02Q}-V_{0XX}| < \Delta V_{OUT-ACCEPTABLE}$

The CMFB Loop

Do a small-signal analysis, only input is  $V_{\text{COFF}}$

$$V_{02} = (V_{02}A + V_{COFF})A_{COM2}$$

$$V_{02} = V_{COFF} \frac{A_{COM2}}{1 - AA_{COM2}}$$

$$\Delta V_{0UT-ACCEPTABLE} = V_{COFF} \frac{A_{COM2}}{1 - AA_{COM2}}$$

- Node Y is common to both differential feedback loop and CMFB loop

- This does not require a particularly large gain

- This is the loop that must be compensated since A and A<sub>COMP2</sub> will be frequency dependent

- Miller compensation capacitor for compensation of differential loop will often appear in shunt with C<sub>2</sub>

- Can create this "half-circuit" loop (without CM inputs on a fully differential structure) for simulations

- Results extend readily to two-stage structures with no big surprises

- Capacitances on nodes X and Y as well as compensation C in A amplifier (often same as capacitor on X node) create poles for CMFB circuit

- Reasonably high closed-loop CMFB bandwidth needed to minimize shifts in output due to high-frequency common-mode noise

#### Compensation of CMFB loop will affect differential compensation if C<sub>2</sub> needs to be changed

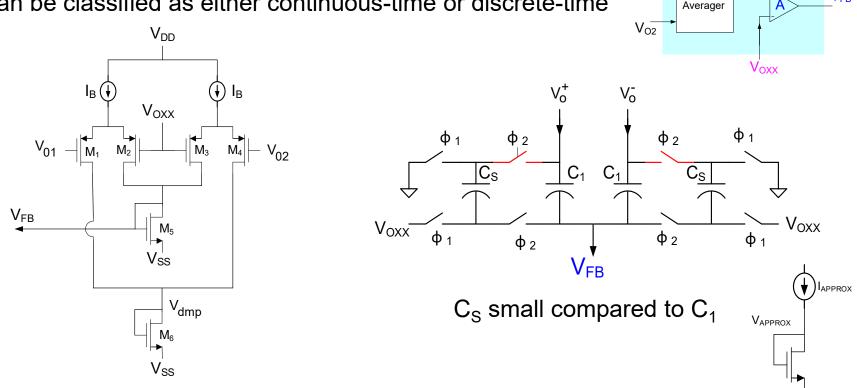

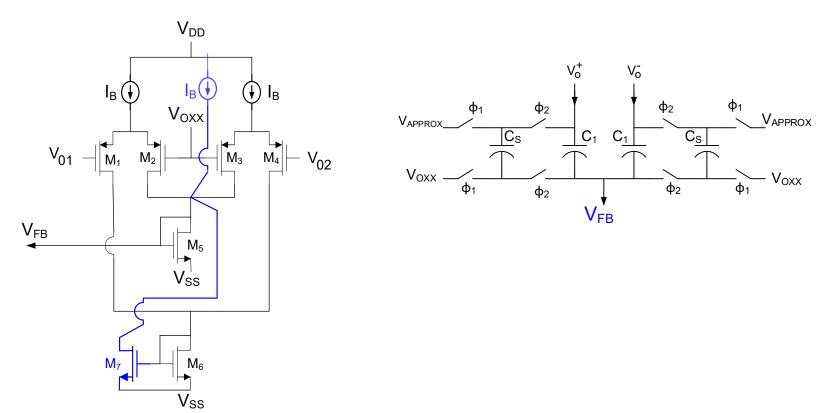

# **CMFB** Circuits

**CMFB Block**

VAVG

$V_{FB}$

$V_{01}$

- Several (but not too many) CMFB blocks are widely used

- Can be classified as either continuous-time or discrete-time

- V<sub>OXX</sub> generated by simple bias generator

- $\varphi_1$  and  $\varphi_2$  are complimentary non-overlapping clocks that run continuously

- At this point, think of  $V_{dmp}$  as a place to "dump" the current from the diff pairs ٠

- But  $V_{dmp}$  does contain the same information as  $V_{FB}$ , only of opposite sign!

## **CMFB** Circuits

Several (but not too many) CMFB circuits exist Can be classified as either continuous-time or discrete-time

Circuit in blue can be added to double CMFB gain

## Stay Safe and Stay Healthy !

#### End of Lecture 23